Ahead-looking: Only a few digital gadgets used right here on Earth can survive once they go away the planet’s comfy environment. Processors, specifically, have to be designed to resist the cruel situations of outer area, together with radiation and near-absolute zero temperatures. It seems that RISC-V might assist handle this problem.

Researchers on the Swiss public college ETH Zurich have developed Trikarenos, a RISC-V-based microcontroller designed to function reliably in harsh environments like area. Trikarenos can stand up to radiation-induced single occasion upsets (SEUs), that are modifications within the state of a micro-electronic machine brought on by a single ionizing particle. Moreover, it could ship efficiency ranges similar to conventional “area chips” whereas consuming solely a fraction of the identical power price range.

Frequent countermeasures to area situations normally depend on proprietary, radiation-hardened applied sciences, low-density manufacturing nodes, and intensive replication, as defined by the researchers. These components contribute to excessive prices and low ranges of efficiency and effectivity. Trikarenos goals to handle these challenges with a 32-bit RISC-V CPU structure and “superior” 28nm manufacturing know-how supplied by TSMC.

The 28nm node has demonstrated resilience to the “damaging results” of radiation-induced SEU occasions, in keeping with the researchers, and it presents unprecedented ranges of effectivity in comparison with earlier designs. Trikarenos makes use of the ultra-low energy PULPissimo microcontroller structure, which is open supply, identical to the RISC-V CPU structure.

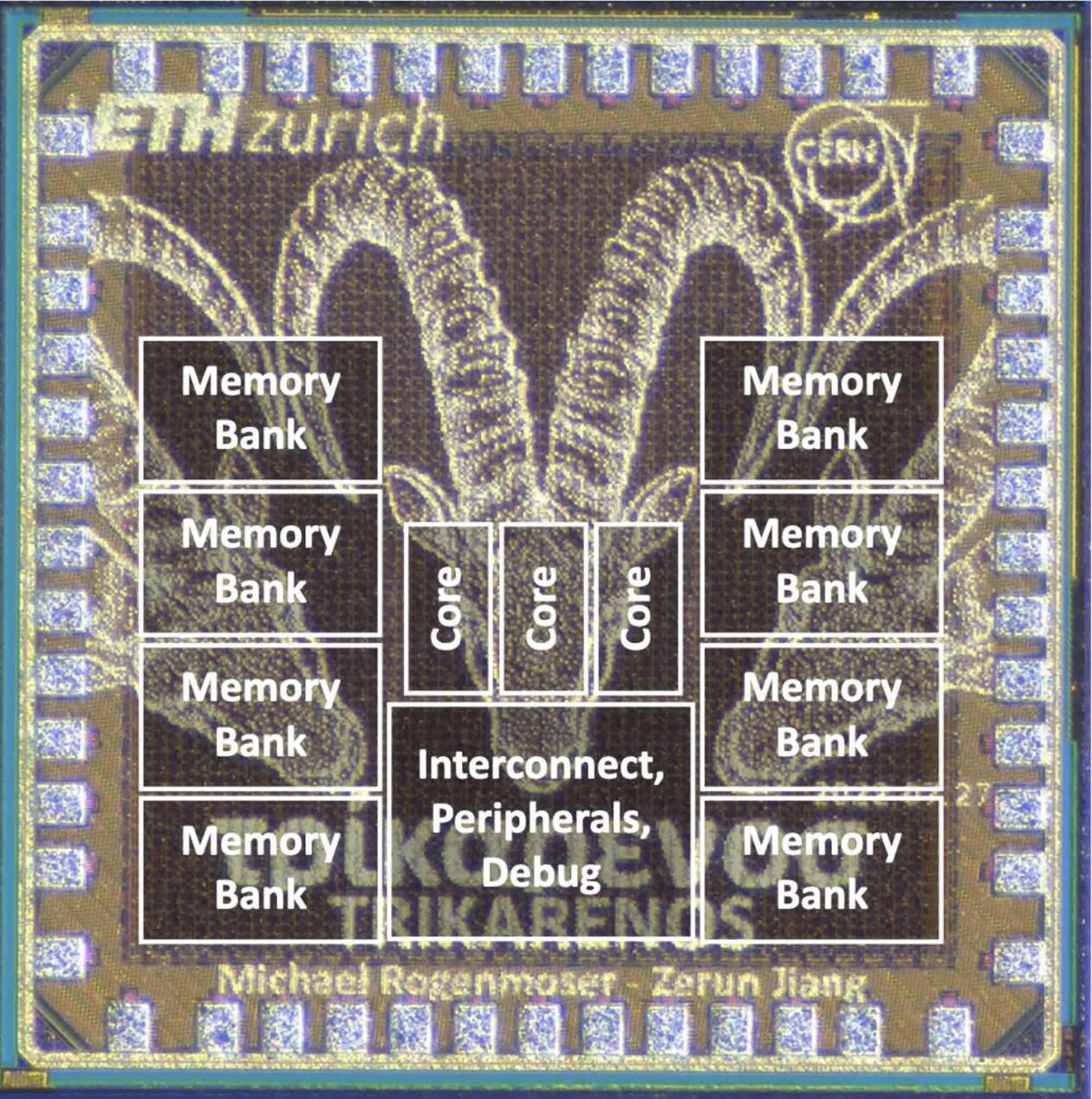

The chip incorporates three RISC-V-based Ibex computing cores, every clocked at speeds of as much as 270 MHz, and they’re provided with information by eight SRAM banks, every with 256 KB of reminiscence. These three cores function in a “triple-core lockstep” configuration, the place every core performs the identical operation concurrently. Within the occasion of an SEU occasion corrupting one of many cores, a vote just like the one depicted in Minority Report would decide the proper operation output.

Different architectural parts designed to reinforce radiation tolerance embrace built-in redundancy, error-correcting reminiscence banks, and a “reminiscence scrubber” that constantly reads every reminiscence handle to right any correctable errors. Moreover, the three Ibex cores are bodily separated by a 20-micrometer hole round every core.

The three-core design presents elevated fault tolerance however could impression the potential efficiency of the controller. However, the design seems able to delivering efficiency ranges similar to the PowerPC-based RAD750 chip, which has been in use for 20 years and continues to be employed by main area businesses for his or her most advanced missions, such because the James Webb Area Telescope. Within the coming years, NASA intends to interchange RAD750 with a high-performance RISC-V CPU designed by SiFive.

Compared to RAD750, which consumes 5 watts of energy, Trikarenos can obtain the identical computing outcomes with simply 15.7 milliwatts, making it advantageous for energy-constrained missions like CubeSat satellite tv for pc launches. If excessive reliability will not be a requirement, the three cores can function in parallel, offering 300 p.c the efficiency of a triple-core lockstep design.