By means of the trying glass: Many advances in semiconductor expertise hinge on lowering package deal sizes whereas incorporating added performance and extra environment friendly energy supply strategies. Current strategies of energy supply eat vital house on the wafer, resulting in elevated prices, bigger die sizes, and fewer transistors. Earlier this yr, Samsung Semiconductor offered its analysis on an alternative choice to typical semiconductor energy supply strategies: bottom energy supply. This might result in vital reductions in die measurement and decreased routing congestion.

Based on a report from TheElec and Samsung’s presentation at this yr’s Very Massive Scale Integration (VLSI) Symposium, the semiconductor producer used new bottom energy supply community (BS-PDN) approaches to efficiently scale back the required wafer space by 14.8% when in comparison with conventional entrance facet energy supply networks (PDNs).

The profitable implementation additionally yielded 10.6% and 19% space reductions in two ARM circuits whereas lowering wiring size by 9.2%.

In conventional frontside PDNs (FSPDNs), semiconductor elements should be organized on the entrance facet of the wafer with a purpose to present transmission from the facility line to the sign line and to the transistors.

This configuration requires shared house and assets between the supply and sign networks, more and more resistant routing to hold electrons throughout the back-end-of-line stack, and may end up in vitality loss throughout transmission to floor rails within the semiconductor construction.

BS-PDN (Bottom Energy Supply Community) is designed to handle these architectural and energy supply limitations. The strategy utterly decouples the facility supply and sign networks and makes use of the bottom of the wafer to accommodate energy distribution. Utilizing the bottom of the wafer, Samsung and different semiconductor producers can as a substitute direct energy supply by shorter, wider traces that supply much less resistance, improved energy supply efficiency, and diminished routing congestion.

Whereas the transfer from FSPDN to BS-PDN sounds promising, there are a number of challenges that forestall it from turning into a typical strategy for producers pursuing the expertise.

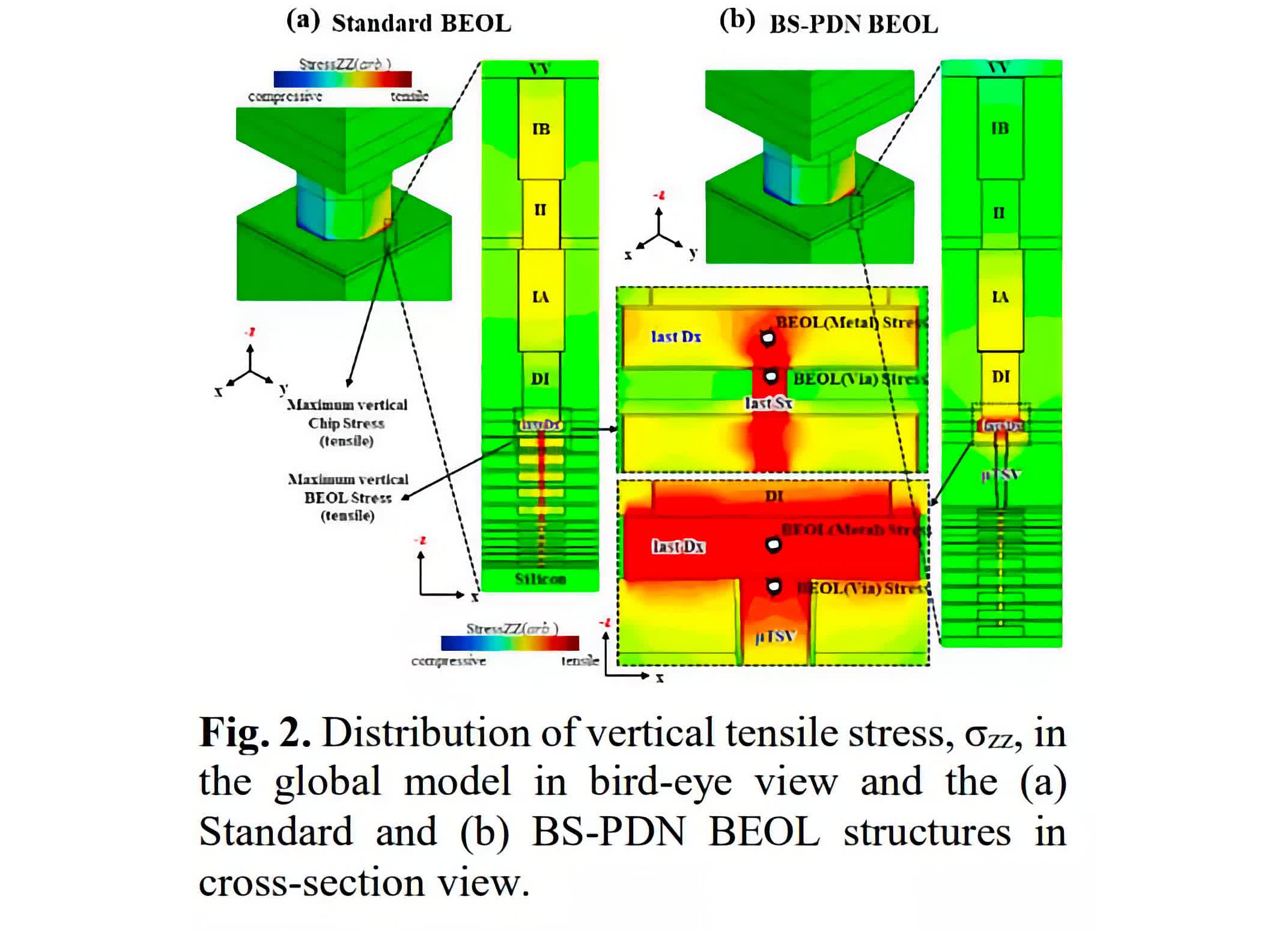

One of many largest challenges to implementing the brand new energy supply mannequin, additionally offered by Samsung on the symposium, is the potential discount in tensile power related to BS-PDN. When utilized, BS-PDN can scale back the tensile stress acts and through-silicon by way of electrode (TSV), leading to separation from the steel layer.

Samsung stated that this drawback may be solved by lowering the peak or widening the TSV, nevertheless extra analysis and testing is required earlier than an answer may be formally introduced. Further advances in sign and energy line connectivity will even be required to efficiently apply BS-PDN.

Along with the above, advances in chemical mechanical sprucing (CMP) expertise would even be required. Present CMP implementations are used to take away 5 to 10 microns of “peaks and valleys” from the bottom of a wafer. Implementing BS-PDN may require a brand new solution to polish the wafer with out damaging the underlying energy elements.

Samsung doesn’t have a present timeline outlining official implementation of BS-PDN-based architectures, however primarily based on present findings and challenges, it isn’t but clear if we’ll see BS-PDN implementations from Samsung, or different producers like TSMC and Intel, for a number of extra years.

Picture supply: imec-int.com